**TPS23861**

SLUSBX9E -MARCH 2014-REVISED MARCH 2016

# TPS23861 IEEE 802.3at Quad Port Power-over-Ethernet PSE Controller

## **Features**

- IEEE 802.3at Quad Port PSE Controller

- Auto Detect, Classification

- Auto Turn-On and Disconnect

- Efficient 255-mΩ Sense Resistor

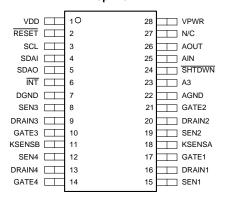

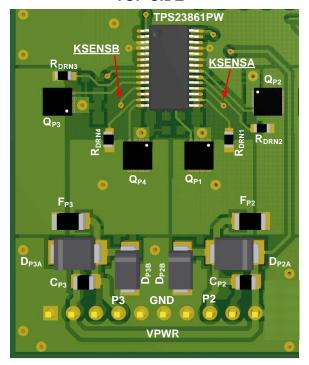

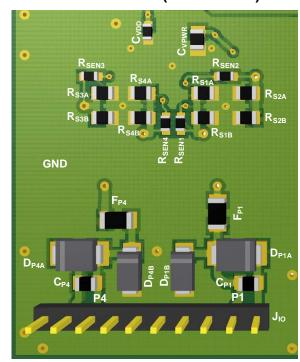

- Pin-Out Enables Two-Layer PCB

- Kelvin Current Sensing

- 4-Point Detection

- Automatic Mode As Shipped

- No External Terminal Setting Required

- No Initial I<sup>2</sup>C Communication Required

- Semi-Automatic Mode Set by I<sup>2</sup>C Command

- Continuous Identification and Classification

- Meets IEEE 400-ms T<sub>PON</sub> Specification

- Fast-Port Shutdown Input

- Operates best when used in conjunction with system reference code http://www.ti.com/product/TPS23861/toolssoftw

- Optional I<sup>2</sup>C Control and Monitoring

- -40°C to 125°C Temperature Range

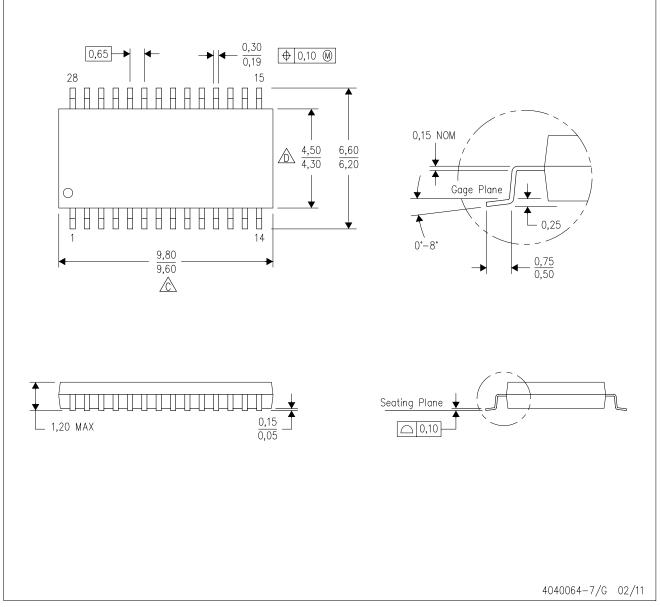

- TSSOP28 Package 9.8 mm x 6.6 mm

# **Applications**

- **Ethernet Switches and Routers**

- Surveillance NVR and DVRs

- Residential Gateways

- PoE Pass-Through Systems

- Wireless Backhaul

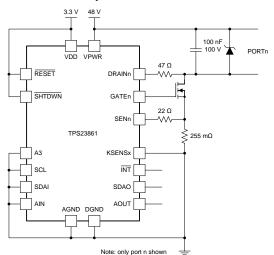

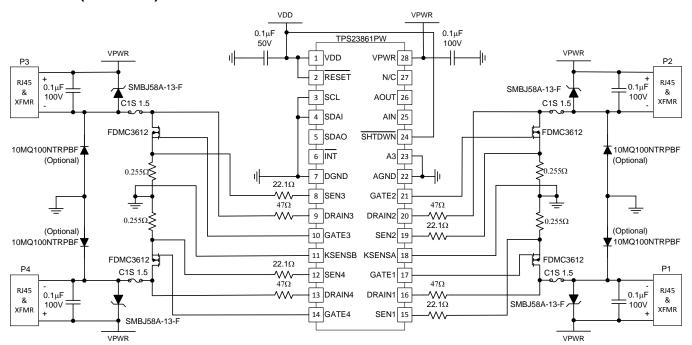

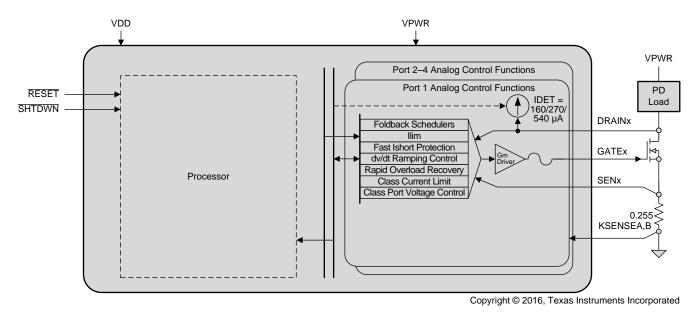

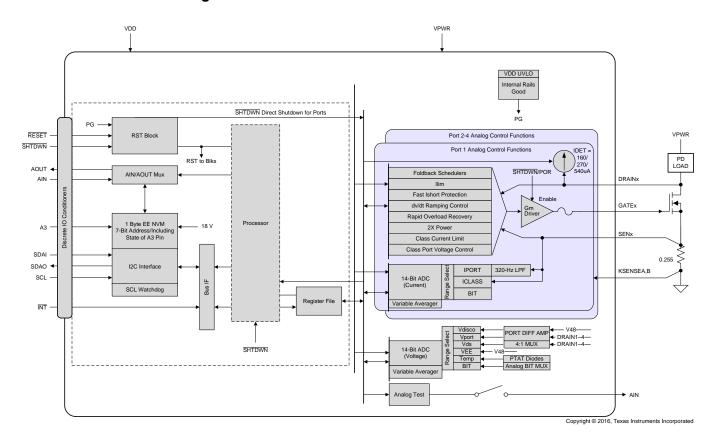

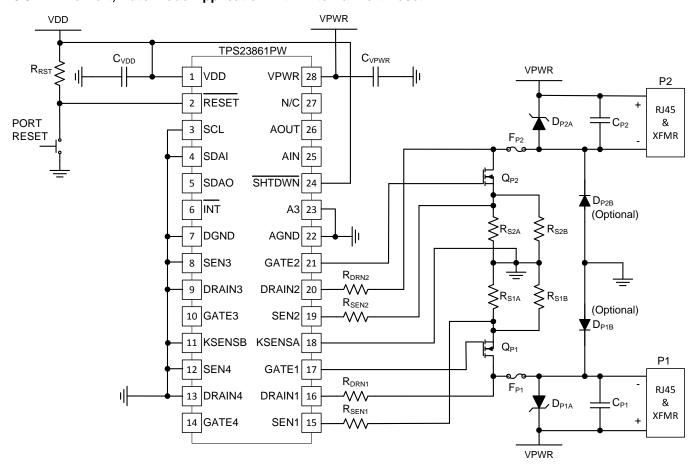

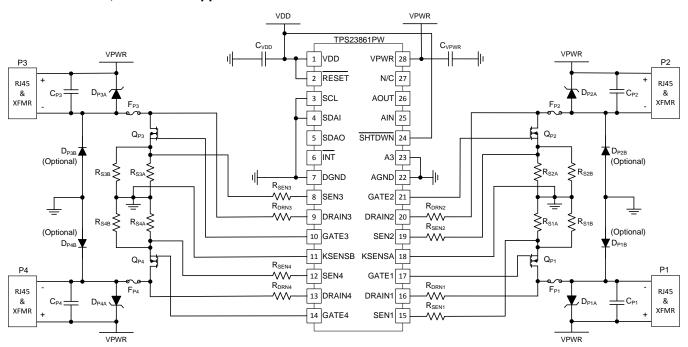

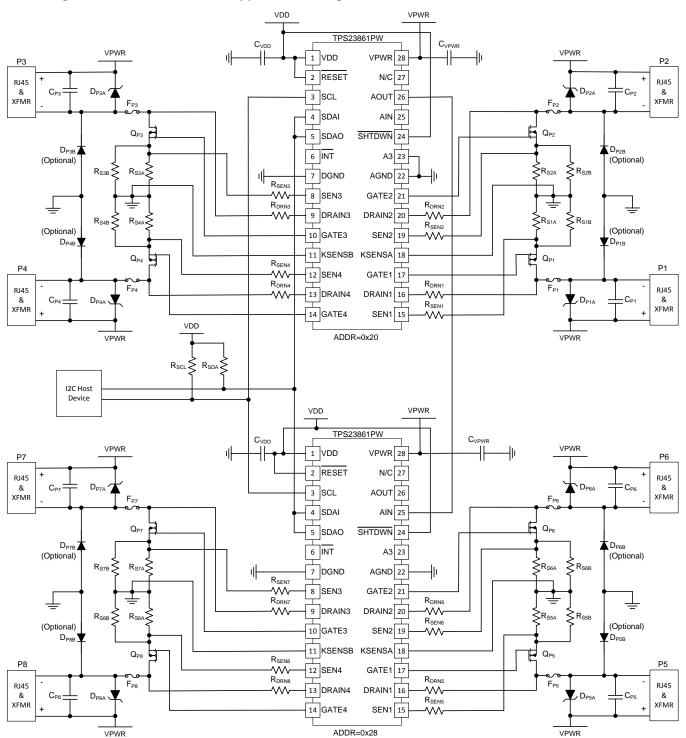

## Simplified Schematic

# 3 Description

TPS23861 The is an easy-to-use. IEEE802.3at PSE solution. As shipped, automatically manages four 802.3at ports without the need for any external control.

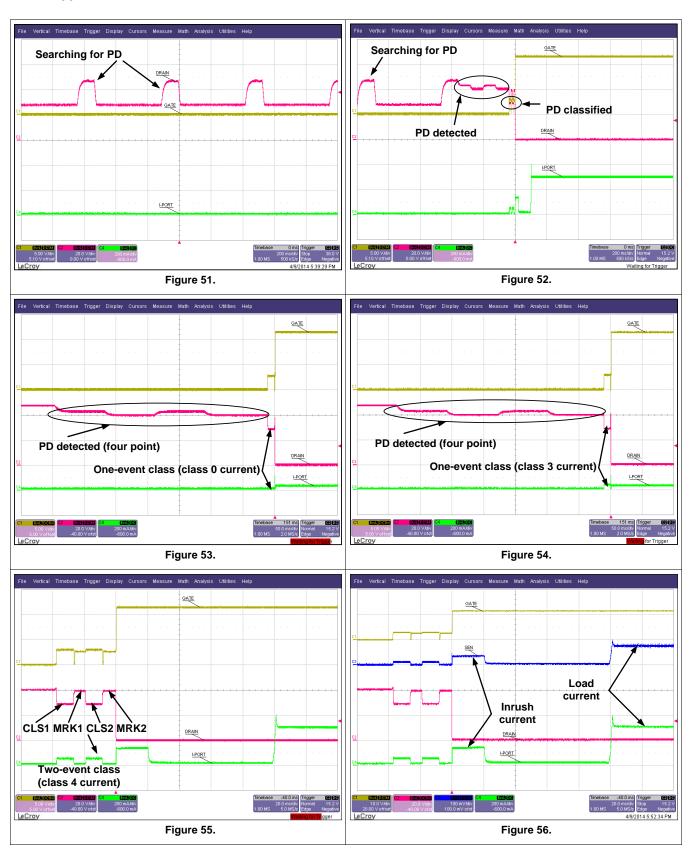

TPS23861 automatically detects Powered Devices (PDs) that have a valid signature, determines power requirements according to classification and applies power. Two-event classification is supported for type-2 PDs. The TPS23861 supports DC disconnection and the external FET architecture allows designers to balance size, efficiency and solution cost requirements.

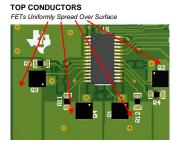

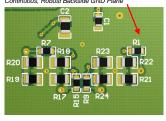

The unique pin-out enables 2-layer PCB designs via logical grouping and clear upper and lower differentiation of  $I^2C$  and power pins. This delivers best-in-class thermal performance, Kelvin accuracy and low-build cost.

In addition to automatic operation, the TPS23861 supports Semi-Auto Mode via I<sup>2</sup>C control for precision monitoring and intelligent power management. Compliance with the 400-ms T<sub>PON</sub> specification is ensured whether in semi-automatic or automatic mode.

### **Device Information**

| ORDER NUMBER | PACKAGE    | BODY SIZE         |

|--------------|------------|-------------------|

| TPS23861PW   | TSSOP (28) | 9.80 mm x 6.60 mm |

BOTTOM GND PLANE Robust Backside GND Plane

# **Table of Contents**

| 1 | Features 1                           | 8  | Application and Implementation                   | 87  |

|---|--------------------------------------|----|--------------------------------------------------|-----|

| 2 | Applications 1                       |    | 8.1 Introduction to PoE                          | 87  |

| 3 | Description 1                        |    | 8.2 Application Information                      | 87  |

| 4 | Revision History2                    |    | 8.3 Typical Application                          | 89  |

| 5 | Pin Configuration and Functions 4    |    | 8.4 System Examples                              | 95  |

| 6 | Specifications5                      | 9  | Power Supply Recommendations                     | 99  |

| U | 6.1 Absolute Maximum Ratings         |    | 9.1 VDD                                          | 99  |

|   | 6.2 ESD Ratings                      |    | 9.2 VPWR                                         | 99  |

|   | 6.3 Recommended Operating Conditions |    | 9.3 VPWR-RESET Sequencing                        | 99  |

|   | 6.4 Thermal Information              | 10 | Layout                                           | 100 |

|   | 6.5 Electrical Characteristics 6     |    | 10.1 Layout Guidelines                           |     |

|   | 6.6 Timing Requirements              |    | 10.2 Layout Example                              | 101 |

|   | 6.7 Switching Characteristics        | 11 | Device and Documentation Support                 |     |

|   | 6.8 Typical Characteristics          |    | 11.1 Documentation Support                       |     |

| 7 | Detailed Description                 |    | 11.2 Community Resources                         |     |

| • | 7.1 Overview                         |    | 11.3 Trademarks                                  | 102 |

|   | 7.2 Functional Block Diagram         |    | 11.4 Electrostatic Discharge Caution             | 102 |

|   | 7.3 Feature Description              |    | 11.5 Glossary                                    |     |

|   | 7.4 Device Functional Modes          | 12 | Mechanical, Packaging, and Orderable Information |     |

|   | To region map 10 / dareboable        |    |                                                  |     |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Chang | ges from Revision D (September 2015) to Revision E                         | Page       |

|-------|----------------------------------------------------------------------------|------------|

| • Ad  | dded note in Features, "Semi-Automatic Mode "                              | 1          |

| • Ali | igned format                                                               | 1          |

| • Up  | odated Pin Functions table                                                 | 4          |

| • Ad  | dded new Figure 37                                                         | 21         |

| • Ad  | ded new Functional Block Diagram                                           | 24         |

| • Ch  | nanged note in A/D Converter and I <sup>2</sup> C Interface                | 33         |

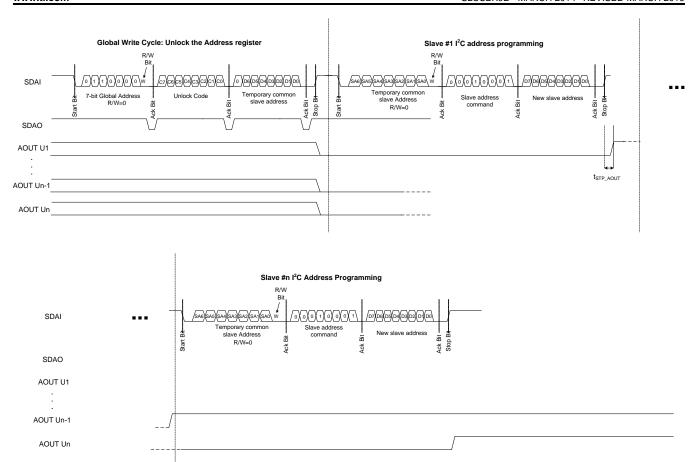

| • Ch  | nanged the Note in I <sup>2</sup> C Slave Address and AUTO Bit Programming | 36         |

| • Ad  | dded note to I <sup>2</sup> C Slave Address and AUTO Bit Programming       | 36         |

| • Ch  | nanged I <sup>2</sup> C slave address register note                        | 36         |

|       | dded new Figure 43                                                         |            |

|       | ded a note to Manual about type 2 power 2 event classification             |            |

|       | dded content to Semi-Auto                                                  |            |

| • Ad  | dded "PoEPn" column to Bits Description                                    | 72         |

| • Ad  | dded a note to PoE Plus Register                                           | <b>7</b> 9 |

| CI | Changes from Revision C (June 2015) to Revision D                                     |    |

|----|---------------------------------------------------------------------------------------|----|

| •  | Added reference note to Figure 5                                                      | 14 |

| •  | Added reference note to Figure 6                                                      | 14 |

| •  | Changed RESET note to add addition reference link.                                    | 22 |

| •  | Added SDAO pin note.                                                                  | 23 |

| •  | Changed I <sup>2</sup> C Slave Address and AUTO Bit Programming note.                 | 36 |

| •  | Added Figure 42, I <sup>2</sup> C/SMBus Interface Slave Address Programming Protocol. | 39 |

| www | .tı | .co | m |

|-----|-----|-----|---|

| Changes from Revision B (April 2015) to Revision C         Page           • Added Figure 5         14           • Added Figure 6         14           • Changed Figure 36, Disconnected AIN pin from GND         21           • Added Figure 36, Disconnected AIN pin from GND         22           • Added Device Power On Initialization section         46           • Added Device Power On Initialization section         46           • Added Power Device Power On Initialization section         46           • Added Power Device Power On Initialization section         46           • Added Power Device Power On Initialization section         46           • Added Power Device Power On Initialization section         46           • Added Power Inable 10         47           • Added Power In Status Register Command note         57           • Added Operating Mode Register Command note         66           • Added Detect/Class Restart Register Command note         66           • Added Detect/Class Restart Register Command note         67           • Added Power Enable Register Bit Descriptions note         67           • Added Power Enable Register Bit Descriptions note         67           • Added Reset Register Bit Descriptions note         68           • Changed Figure 48, Disconnected AIN pin from GND         80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                            | Added note 3 to Table 10                                                                |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|------------|

| Added Figure 5     Added Figure 6     Added Figure 6     Added Figure 8     Added SHTDWN note.     Added SHTDWN note.     Added BESET note.     Added Device Power On Initialization section.     Added Device Power On Initialization section.     Added Operating Mode Register note.     Added Operating Mode Register Command note.     Added Operating Mode Register Command note.     Added Operating Mode Register Experience.     Added Detect/Class Enable Register Command note.     Added Detect/Class Enable Register Command note.     Added Power Enable Register Command note.     Added Power Enable Register Command note.     Added Power Enable Register Description sote.     Added Reset Register Experience.     Added Reset Register Command note.     Added Reset Register Bit Descriptions note.     Added Reset Register Bit Descriptions note.     Added Reset Register Bit Descriptions note.     Changed Figure 48, Disconnected AIN pin from GND.     Changed Figure 48, Disconnected AIN pin from GND.     Changed Figure 49, Disconnected AIN pin from GND.     Changed Figure 49, Disconnected AIN pin from GND.     Changed Figure 50, Disconnected AIN pin from GND.     Changed Figu | •                                            | Changed Connections on Unused Ports section                                             | 88         |

| Added Figure 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                            | Added reference link to the VPWR-RESET Sequencing note.                                 | 99         |

| <ul> <li>Added Figure 6</li> <li>Changed Figure 36, Disconnected AIN pin from GND.</li> <li>Added SHTDWN note.</li> <li>Added RESET note.</li> <li>Added Device Power On Initialization section.</li> <li>Added Operating Mode Register Note.</li> <li>Added Operating Mode Register Command note.</li> <li>Added Operating Mode Register Bit Description note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Added VPWR-RESET Sequencing.</li> <li>Peleted Proce</li></ul>                                                                                                                                  | Ch                                           | nanges from Revision B (April 2015) to Revision C                                       | Page       |

| <ul> <li>Changed Figure 36, Disconnected AIN pin from GND</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Added Figure 5                                                                          | 14         |

| <ul> <li>Added SHTDWN note</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                            | Added Figure 6                                                                          | 14         |

| <ul> <li>Added RESET note.</li> <li>Added Device Power On Initialization section.</li> <li>Added note 2 to Table 10.</li> <li>Added Port n Status Register note.</li> <li>Added Operating Mode Register Command note.</li> <li>Added Operating Mode Register Bit Description note.</li> <li>Added Operating Mode Register Command note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AlN pin from GND.</li> <li>Changed Figure 48, Disconnected AlN pin from GND.</li> <li>Changed Figure 49, Disconnected AlN pin from GND.</li> <li>Changed Figure 50, Disconnected AlN pin from GND.</li> <li>Changed Q<sub>Pn</sub> description in Per Port Components</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing</li> <li>Changes from Revision A (June, 2014) to Revision B</li> <li>Page</li> <li>Changed Figure 10 consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the 1°C interface note.</li> <li>Added When using the 1°C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical)</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                            | Changed Figure 36, Disconnected AIN pin from GND                                        | 21         |

| <ul> <li>Added Device Power On Initialization section</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                            | Added SHTDWN note.                                                                      | 22         |

| <ul> <li>Added note 2 to Table 10</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                            | Added RESET note.                                                                       | 22         |

| <ul> <li>Added Port n Status Register note.</li> <li>Added Operating Mode Register Command note.</li> <li>Added Operating Mode Register Bit Description note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Command note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Rigure 50, Disconnected AIN pin from GND.</li> <li>Changed Nescription in Per Port Components.</li> <li>Changed Tigure 50, Disconnected AIN pin from GND.</li> <li>Changed Type Port Components.</li> <li>Changed Type Port Components.</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                          | •                                            | Added Device Power On Initialization section                                            | 46         |

| <ul> <li>Added Operating Mode Register Command note.</li> <li>Added Operating Mode Register Bit Description note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Command note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Mescription in Per Port Components.</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing.</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I²C interface note.</li> <li>Added When using the I²C interface note.</li> <li>Changed LSB VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                            | Added note 2 to Table 10                                                                | 47         |

| <ul> <li>Added Operating Mode Register Bit Description note.</li> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Command note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Q<sub>Pn</sub> description in Per Port Components</li> <li>Changed Maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing.</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX).</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> <li>73</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                            | Added Port n Status Register note.                                                      | 57         |

| <ul> <li>Added Detect/Class Enable Register Command note.</li> <li>Added Detect/Class Restart Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Command note.</li> <li>Added Power Enable Register Bit Descriptions note.</li> <li>Added Reset Register Command note.</li> <li>Added Reset Register Command note.</li> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Pigure 50, Disconnected AIN pin from GND.</li> <li>Changed QPn description in Per Port Components</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing.</li> <li>Changed From Revision A (June, 2014) to Revision B</li> <li>Page</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                            | Added Operating Mode Register Command note.                                             | 60         |

| <ul> <li>Added Detect/Class Restart Register Command note</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Added Operating Mode Register Bit Description note.                                     | 60         |

| <ul> <li>Added Power Enable Register Command note</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                            | Added Detect/Class Enable Register Command note.                                        | 61         |

| <ul> <li>Added Power Enable Register Bit Descriptions note</li> <li>Added Reset Register Command note</li> <li>Added Reset Register Command note</li> <li>Added Reset Register Bit Descriptions note</li> <li>Changed Figure 46, Disconnected AIN pin from GND</li> <li>Changed Figure 48, Disconnected AIN pin from GND</li> <li>Changed Figure 49, Disconnected AIN pin from GND</li> <li>Changed Figure 50, Disconnected AIN pin from GND</li> <li>Changed Q<sub>Pn</sub> description in Per Port Components</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD</li> <li>Added VPWR-RESET Sequencing</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification</li> <li>Added When using the I<sup>2</sup>C interface note</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical)</li> <li>Changed LSB VALUE from 0.652°C to 7°C</li> <li>73</li> <li>Changed LSB VALUE from 0.652°C to 7°C</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                            | Added Detect/Class Restart Register Command note.                                       | 66         |

| <ul> <li>Added Reset Register Command note</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                            | Added Power Enable Register Command note                                                | 67         |

| <ul> <li>Added Reset Register Bit Descriptions note.</li> <li>Changed Figure 46, Disconnected AIN pin from GND.</li> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Q<sub>Pn</sub> description in Per Port Components</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX).</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                            | Added Power Enable Register Bit Descriptions note.                                      | 67         |

| <ul> <li>Changed Figure 46, Disconnected AIN pin from GND</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Added Reset Register Command note                                                       | 68         |

| <ul> <li>Changed Figure 48, Disconnected AIN pin from GND.</li> <li>Changed Figure 49, Disconnected AIN pin from GND.</li> <li>Changed Figure 50, Disconnected AIN pin from GND.</li> <li>Changed Q<sub>Pn</sub> description in Per Port Components.</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing.</li> <li>Changes from Revision A (June, 2014) to Revision B</li> <li>Page</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX).</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> <li>73</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Added Reset Register Bit Descriptions note.                                             | 68         |

| <ul> <li>Changed Figure 49, Disconnected AIN pin from GND</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Changed Figure 46, Disconnected AIN pin from GND                                        | 87         |

| <ul> <li>Changed Figure 50, Disconnected AIN pin from GND</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                            | Changed Figure 48, Disconnected AIN pin from GND                                        | 89         |

| <ul> <li>Changed Q<sub>Pn</sub> description in Per Port Components</li> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing</li> <li>Changes from Revision A (June, 2014) to Revision B</li> <li>Page</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                            | Changed Figure 49, Disconnected AIN pin from GND                                        | 90         |

| <ul> <li>Changed maximum VDD supply current from 10 mA to 6 mA in first paragraph and changed wording in second paragraph of VDD.</li> <li>Added VPWR-RESET Sequencing</li> <li>Changes from Revision A (June, 2014) to Revision B</li> <li>Page</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I²C interface note.</li> <li>Added When using the I²C interface note.</li> <li>Added When using the I²C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                            | Changed Figure 50, Disconnected AIN pin from GND                                        | 91         |

| paragraph of VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                            | Changed Q <sub>Pn</sub> description in Per Port Components                              | 92         |

| <ul> <li>Added VPWR-RESET Sequencing</li> <li>Changes from Revision A (June, 2014) to Revision B</li> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)</li> <li>Deleted Processor watchdog trip delay specification</li> <li>Added When using the I<sup>2</sup>C interface note</li> <li>Added When using the I<sup>2</sup>C interface note</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical)</li> <li>Changed LSB VALUE from 0.652°C to 7°C</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                            |                                                                                         | 99         |

| <ul> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX).</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                            |                                                                                         |            |

| <ul> <li>Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX).</li> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |                                                                                         |            |

| <ul> <li>Deleted Processor watchdog trip delay specification.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ch                                           | nanges from Revision A (June, 2014) to Revision B                                       | Page       |

| <ul> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                            | Changed VDD current consumption from 10 mA (MAX) to 6.0 mA (MAX)                        | 6          |

| <ul> <li>Added When using the I<sup>2</sup>C interface note.</li> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                            | Deleted Processor watchdog trip delay specification.                                    | 10         |

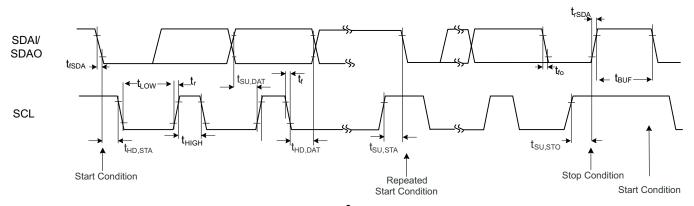

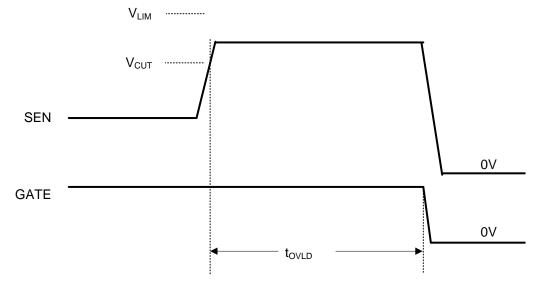

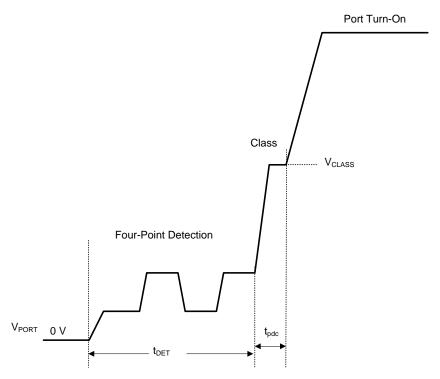

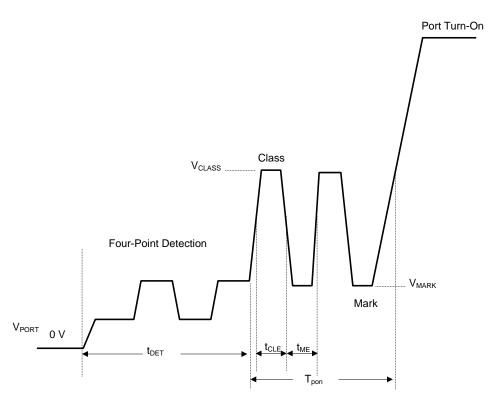

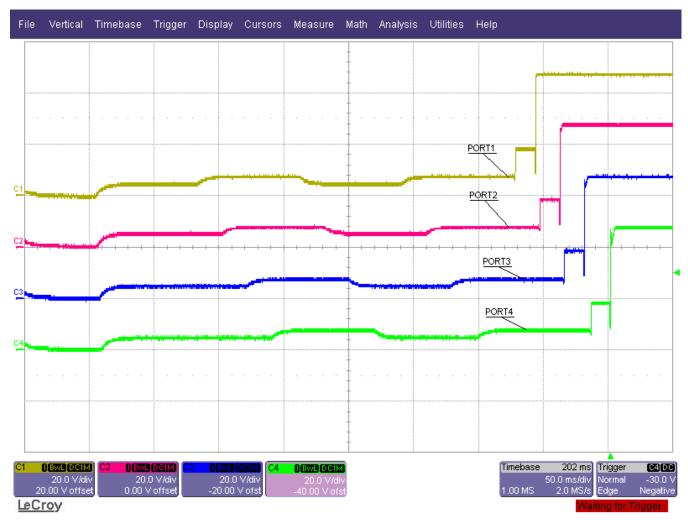

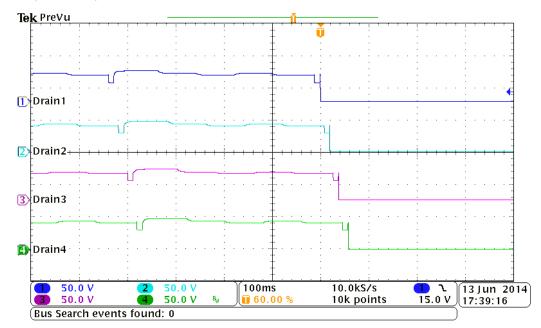

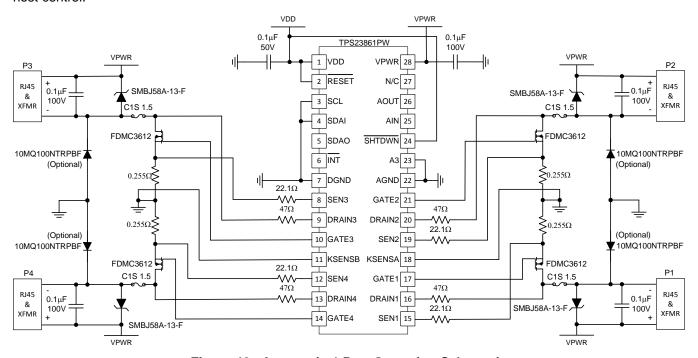

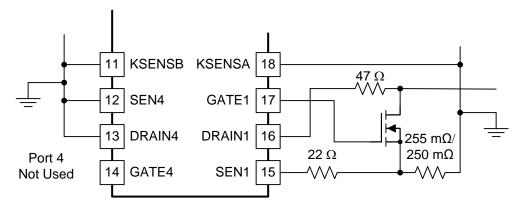

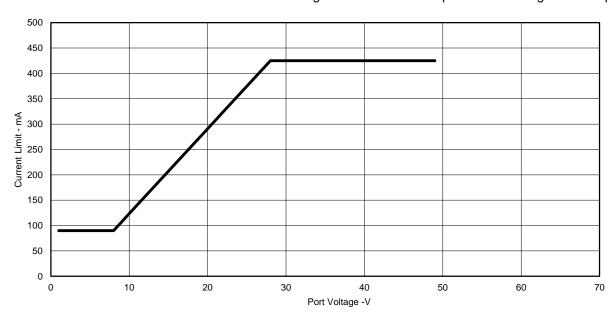

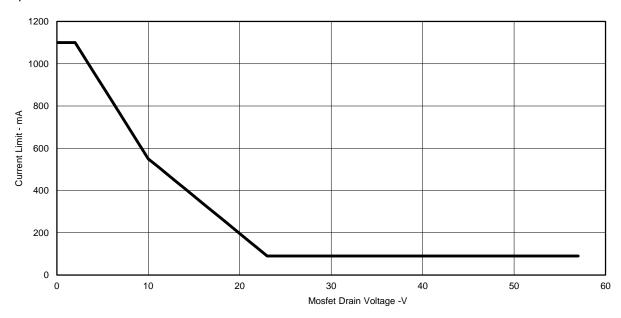

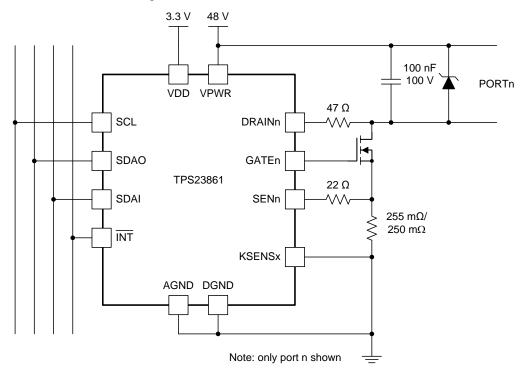

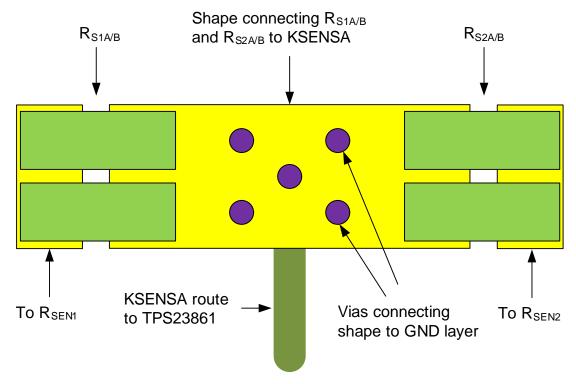

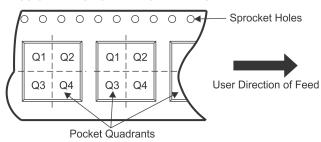

| <ul> <li>Changed FULL SCALE VALUE from 146.2°C to 150°C (typical).</li> <li>Changed LSB VALUE from 0.652°C to 7°C.</li> <li>73</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                            | Added When using the I <sup>2</sup> C interface note.                                   | 33         |